全球晶圓代工巨頭台積電在舊金山舉行的 IEEE 國際電子器件會議 (IEDM) 上,公佈了備受矚目的 2 納米(N2)製程技術的更多細節資料。向媒體展示了新技術在性能、功耗以及晶體管密度方面的顯著進步。

全球晶圓代工巨頭台積電在舊金山舉行的 IEEE 國際電子器件會議 (IEDM) 上,公佈了備受矚目的 2 納米(N2)製程技術的更多細節資料。向媒體展示了新技術在性能、功耗以及晶體管密度方面的顯著進步。

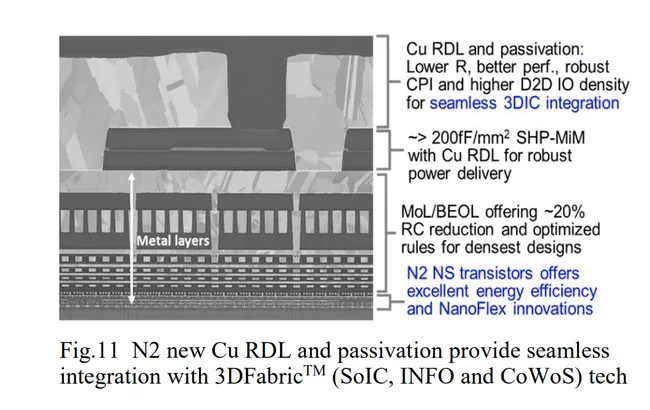

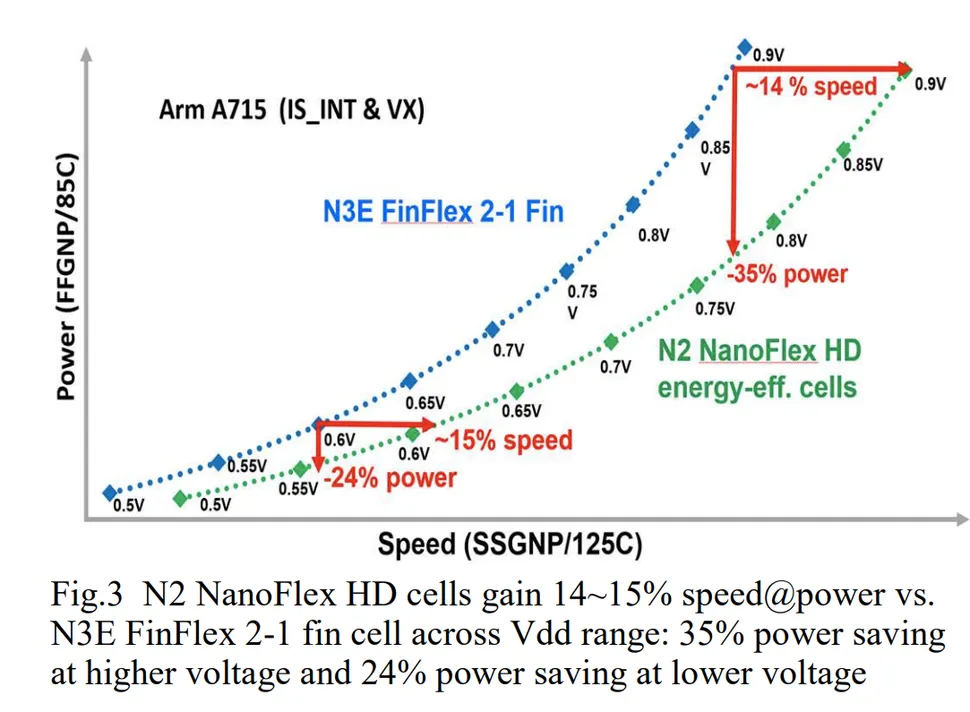

台積電在會議上著重介紹了 2nm「納米片(nanosheets)」技術。官方表示新製程相對於前代製程,性能提升 15%,功耗卻降低高達 30%,能效提升顯著。此外,由於應用了環繞式柵極(GAA)納米片晶體管和 N2 NanoFlex 技術,實現了晶體管密度提高 1.15 倍。N2 NanoFlex 技術允許製造商在最小的面積內集成不同的邏輯單元,能進一步優化製程性能。

台積電在會議上著重介紹了 2nm「納米片(nanosheets)」技術。官方表示新製程相對於前代製程,性能提升 15%,功耗卻降低高達 30%,能效提升顯著。此外,由於應用了環繞式柵極(GAA)納米片晶體管和 N2 NanoFlex 技術,實現了晶體管密度提高 1.15 倍。N2 NanoFlex 技術允許製造商在最小的面積內集成不同的邏輯單元,能進一步優化製程性能。

從當前傳統的 FinFET(鰭式場效應晶體管)技術過渡到專用的 N2「納米片」技術,採用堆疊的窄硅帶結構,讓每條硅帶都被柵極包圍,相比 FinFET 技術,能更精確對電流進行控制。製造商可以結合不同場景來微調參數,有效提升功耗表現。

從當前傳統的 FinFET(鰭式場效應晶體管)技術過渡到專用的 N2「納米片」技術,採用堆疊的窄硅帶結構,讓每條硅帶都被柵極包圍,相比 FinFET 技術,能更精確對電流進行控制。製造商可以結合不同場景來微調參數,有效提升功耗表現。

除此之外, N2 製程對比 3nm 及其衍生製程,在性能的表現上有顯著的提升。因為其優異的表現,猜測包括 Apple 和 NVIDIA 在內的行業巨頭會陸續大規模採用 N2 製程。

新工藝對晶圓的加工要求更高,晶圓的價格也會跟著上漲。N2 製程晶圓的價格將會比 3nm 製程高出 10% 以上。目前 3nm 晶圓的價格約為 2萬美元,N2 晶圓的價格可能在 2.5 萬至 3 萬美元之間(具體取決台積電的定價)。結合前期 N2 製程良率和試生產等因素,N2 製程的初期產量和成本都會受到限制。