目前高科技產品都離不開「心臟」——晶片,但是目前電子產品更新速度越來越快,而與之相反的是晶片的迭代周期開始跟不上。為了能夠保證晶片的快速迭代,必須縮短設計週期。

Google 團隊為了縮短晶片設計週期,將 AI 強化學習方法運用其中,EDA 巨頭 Synopsys 和 Cadence 也是推出了類似的工具。

Google 團隊為了縮短晶片設計週期,將 AI 強化學習方法運用其中,EDA 巨頭 Synopsys 和 Cadence 也是推出了類似的工具。

目前 AI 晶片的開發需要投入大量資金和時間,通常需要幾年的時間完成研發,難以滿足 AI 算法更新需求。為了這個矛盾,Google 做了一個大膽的決定,讓 AI 來設計 AI 晶片。

在 Arxiv 網站上有一篇論文稱「我們相信,AI 將能夠縮短晶片的設計週期,在硬件與 AI 算法之間建立共生關係,並進一步推動彼此的進步。我們已經看到,有些算法或神經網絡架構在現有的 AI 加速器上效果不佳,因為加速器設計類似於兩年前,而那時這些神經網絡架構和算法並不存在。」還有 Google 高級研究科學家 Azalia Mirhoseini 稱「如果縮短設計週期,我們可以縮小差距。」

在 Arxiv 網站上有一篇論文稱「我們相信,AI 將能夠縮短晶片的設計週期,在硬件與 AI 算法之間建立共生關係,並進一步推動彼此的進步。我們已經看到,有些算法或神經網絡架構在現有的 AI 加速器上效果不佳,因為加速器設計類似於兩年前,而那時這些神經網絡架構和算法並不存在。」還有 Google 高級研究科學家 Azalia Mirhoseini 稱「如果縮短設計週期,我們可以縮小差距。」

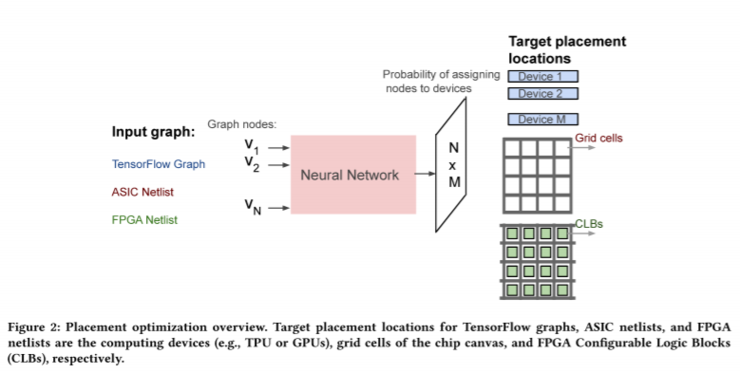

晶片開發最耗費時間的是「佈局」,Mirhoseini 和高級軟件工程師 Anna Goldie 提出了一個神經網絡,是通過對晶片的長時間學習,使其能夠在 24小時內設計好 Google Tensor 處理單元,並且在功耗、性能、面積上超過了專家數週的研究成果。

值得注意的是,Goldie 和 Mirhoseini 的 AI 佈局建模為強化學習問題,不是通過大量數據來進行訓練學習,而是讓 AI 邊做邊學習。這樣設計的好處是能夠有效調節參數,降低功率等,並且隨著設計的越多,呈現的效果會更好。

兩大 EDA 公司也推出了相應的工具。 Synopsys 的自主 AI 晶片設計程式 DSO.ai(Design Space Optimization AI)。是通過晶片設計產生大數據流,隨著時間演變,調整設計,讓設計向多維優化目標發展。 Cadence 為新版 Cadence 數碼全流程,支援機器學習(ML)功能,實習統一佈局佈線和物理優化引擎等多項業界首創技術,在吞吐量上最高提升 3倍,PPA 最高提升20%。

隨著 AI 技術的發展,不知道還會帶來什麼樣的便捷,真是科技改變生活。